Difference between SAP 1 and SAP 2

Key Difference: SAP 1 stands for Simple As Possible 1 and similarly SAP 2 stands for Simple As Possible 2. SAP 1 defines the basic model design of a microprocessor. SAP 2 is the enhanced version of SAP 1 which provides better computing capabilities.

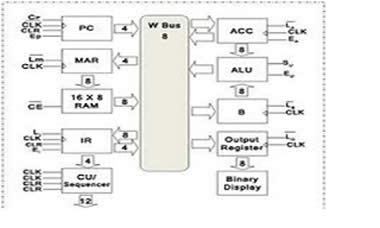

SAP in SAP 1 and SAP 2 stands for Simple As Possible. Both refer to the models of microprocessors; SAP 2 is a successor to SAP 1. SAP 1 design is one of the basic model designs which fulfill basic requirements of a functional microprocessor. It is able to describe the basic working of a microprocessor.

SAP in SAP 1 and SAP 2 stands for Simple As Possible. Both refer to the models of microprocessors; SAP 2 is a successor to SAP 1. SAP 1 design is one of the basic model designs which fulfill basic requirements of a functional microprocessor. It is able to describe the basic working of a microprocessor.

It also defines the basic interaction mechanism with memory and other parts. It consists of simple and confined instruction set. It makes use of a 16 bytes memory (RAM) and a single 8 bit bus for transfer of data and address. Due to its limited capabilities it is usually used for academic purposes only.

SAP 1 is followed by SAP 2 which is superior model to SAP 1 as many new features are added in this model. The features are implemented through hardware. Although the operations are more or less same, the datapath is bigger in comparison to SAP 1.

SAP 1 is followed by SAP 2 which is superior model to SAP 1 as many new features are added in this model. The features are implemented through hardware. Although the operations are more or less same, the datapath is bigger in comparison to SAP 1.

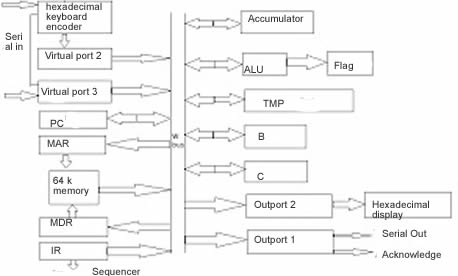

RAM in the case of SAP 2 is 64k. The bus for SAP 2 is 16 bits. Due to the addition of extra registers, the control sequencer is also bigger in comparison to SAP 1. Memory data register in SAP 2 helps to retain the result of a memory access. B register is also now known as TMP in SAP 2. The unit of Adder/ Subtractor is also known as Arithmetic/Logic unit as it also carries out logical tasks rather than just subtraction and addition. The unit also performs logic operations. In SAP 2 the instruction can occur in variable length.

SAP 2 is the enhanced model in comparison to SAP 1 as it includes modern functions. For example - it also includes jump instructions through which certain section of the programs can be repeated or skipped. This feature extends the computing capabilities of the computer.

Comparison between Sap 1 and Sap 2:

|

SAP 1 |

SAP 2 |

|

|

Full Form |

Simple As Possible 1 |

Simple as Possible 2 |

|

Logical operations |

Cannot be handled |

Can be handled |

|

Addresses |

8 bits |

16 bits |

|

Opcodes |

4 bits |

8 bits |

|

Instructions |

Fixed length |

Variable length. |

|

Adder/substactor unit |

Carries out simple operations like addition and subtraction |

Carries out logical operations too and therefore also known as ARITHMETIC/LOGIC UNIT |

|

Size of control sequencer |

Smaller |

Bigger due to extra registers |

|

Number of instructions |

Comparatively lesser |

Comparatively greater |

|

Register to hold the data being added or subtracted from the accumulator |

B |

TMP |

|

Jump instructions |

Not available |

JM, JZ and JNZ – conditional jumps JMP – unconditional jumps |

|

Instructions |

Includes instruction – LDA, ADD, SUB, OUT and HLT |

Includes instructions like ADD, SUB, INR, JMP, DCR, ANA, ORA, XRA, ANI, ORI, XRI, etc. |

|

Display to show outputs in the LEDs |

Binary |

Hexadecimal |

Image Courtesy: pukkaraz.blogspot.in, csit-on-move.blogspot.in

Add new comment